# Audio Multi-function Digital Filter

#### **OVERVIEW**

The SM5843A×1 is a multi-function digital filter IC, fabricated using NPC's Molybdenum-gate CMOS process, for digital audio reproduction equipment. It features 8-times oversampling (interpolation), digital deemphasis and soft muting functions. It accepts 16, 18, or 20-bit input data, and outputs data in 18 or 20-bit format. It operates using either a 384fs or 256fs system clock.

#### **FEATURES**

- Filter configuration (2-channel processing)

- 8-times oversampling (interpolation)

- 3-stage FIR configuration

- · Deemphasis filter

- IIR filter configuration for correct gain and phase characteristics

- 2-channel independent ON/OFF control

- 32/44.1/48 kHz sampling frequency (fs)

- $21 \times 22$ -bit parallel multiplier/25-bit accumulator for high precision

- · Overflow limiter

- 2 oversampling filter characteristics

- Sharp roll-off characteristic (response 1)

- $\le \pm 0.00005$  dB passband ripple (0 to 0.4535fs)

- $\geq$  110 dB stopband attenuation (0.5465fs to 7.4535fs)

- Slow roll-off characteristic (response 2)

- $\le \pm 0.00003$  dB passband ripple (0 to 0.235fs)

- $\ge 77$  dB stopband attenuation (0.745fs to 7.255fs)

- Soft muting

- Digital attenuator

- Input data format

- 2s complement, MSB first

- LR alternating, 16/18/20-bit serial, trailing data

- LR alternating, 20-bit serial, leading data

- LR simultaneous, 20-bit serial, leading data

- Output data format

- 2s complement, MSB first, LR simultaneous

- 18/20-bit serial

- BCKO burst (NPC format)

- Dither processing ON/OFF control

- Jitter-free/Sync mode selectable

- 256fs/384fs system clock selectable

- 21.2/14.2MHz (384fs/256fs)

maximum

frequency

- 5 V supply

- Crystal oscillator circuit built-in

- TTL-compatible input/outputs

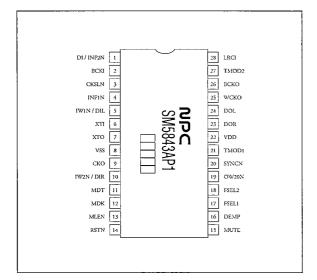

- 28-pin plastic DIP and SOP

- Molybdenum-gate CMOS

#### **APPLICATIONS**

- CD players

- DAT players

- PCM systems

#### ORDERING INFOMATION

| Device    | Package   |

|-----------|-----------|

| SM5843AP1 | 28pin DIP |

| SM5843AS1 | 28pin SOP |

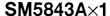

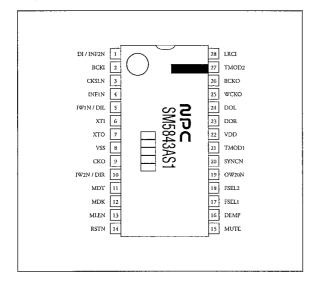

# PINOUT(TOP VIEW)

# 28-pin DIP

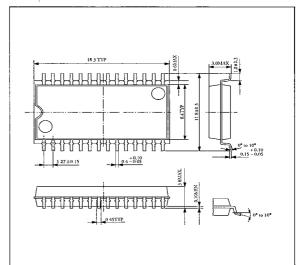

# PACKAGE DIMENSIONS(Unit: mm)

## 28-pin DIP

#### 28-pin SOP

#### 28-pin SOP

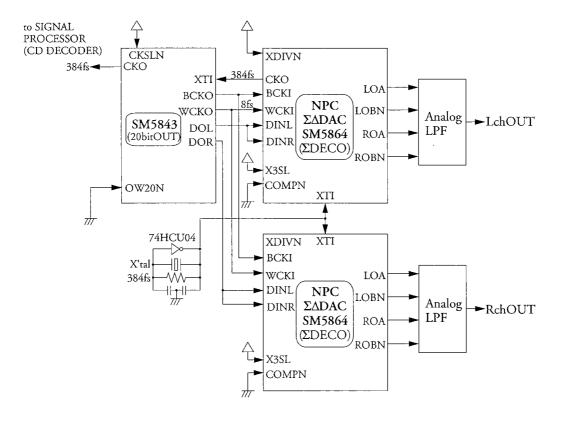

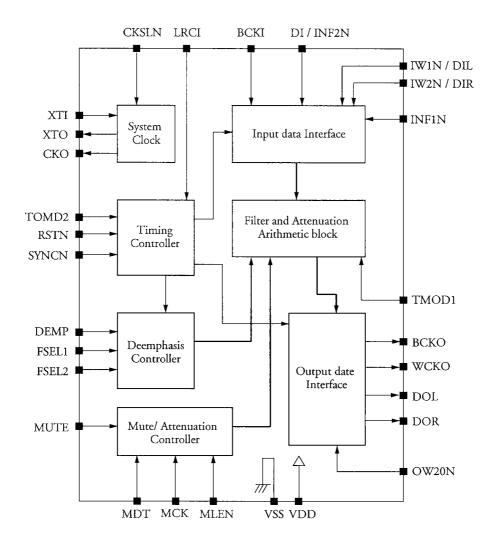

# **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| Number | Name     | I/O <sup>1</sup> |                | Description                                                                        |                                  |                                            |                |               |             |

|--------|----------|------------------|----------------|------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------|----------------|---------------|-------------|

| 1      | DI/INF2N | lp               | Data input w   | hen INF1N is                                                                       | LOW, and inp                     | ut format select pin                       | when INF1N     | is HIGH.      | •           |

| 2      | BCKI     | lp               | Input bit cloc | k                                                                                  |                                  |                                            |                |               |             |

| 3      | CKSLN    | lp               | Oscillator and | d system clo                                                                       | ck select input.                 | 384fs when HIGH,                           | and 256fs w    | nen LOW.      |             |

|        |          |                  | Input format   | select pin. IN                                                                     | F1N and INF2                     | N select the pin fun                       | ctions below.  |               |             |

|        |          |                  | INF1N          | DI/INF2N                                                                           | Inn                              | ut format                                  | Pin 1          | function sele | ection      |

|        |          |                  |                | Di/INI ZIN                                                                         | ""                               | at format                                  | DI/INF2N       | IW1N/DIL      | IW2N/DIR    |

| 4      | INF1N    | lp               | LOW            | LOW                                                                                | I D alterna                      | ting, trailing data                        | DI             | IW1N          | IW2N        |

|        |          |                  | LOW            | HIGH                                                                               | Littatema                        | ung, trailing data                         |                | 144114        | 144214      |

|        |          |                  | HIGH           | LOW                                                                                | LR alterna                       | ting, leading data                         | INF2N          | DIL           | DIR         |

|        |          |                  | HIGH           | HIGH                                                                               | LR simultan                      | eous, leading data                         | INFZIN         | DIL           | DIN         |

|        |          |                  |                |                                                                                    | when INF1N is<br>e input data le | s LOW, and left-cha                        | nnel data inp  | ut when INF1  | N is HIGH.  |

|        |          |                  | INF            | 1N                                                                                 | IW2N/D                           | IL IW                                      | 1N/DIR         | Input b       | oit length  |

|        |          |                  |                |                                                                                    | LOW                              |                                            | LOW            | 20            | ) bits      |

| 5      | lW1N/DIL | lp               | LO             | ,,,                                                                                | LOW                              |                                            | HIGH           | 20            | ) bits      |

|        |          |                  |                | TVV                                                                                | HIGH                             |                                            | LOW            | 18 bits       |             |

|        |          |                  |                |                                                                                    | HIGH                             | HIGH HIGH                                  |                | 16 bits       |             |

|        |          |                  | HIG            | HE                                                                                 | ×                                |                                            | ×              |               | bits        |

| 6      | XTI      | I                | Oscillator inp | out connection                                                                     | n                                |                                            |                |               |             |

| 7      | XTO      | 0                | Oscillator out | tput connecti                                                                      | on                               |                                            |                |               |             |

| 8      | VSS      | _                | Ground         |                                                                                    |                                  |                                            |                |               |             |

| 9      | СКО      | 0                | Oscillator out | tput clock. Sa                                                                     | ıme frequency                    | as XTI.                                    |                |               |             |

| 10     | IW2N/DIR | lp               |                |                                                                                    |                                  | s LOW, and right-ch<br>ngth as shown in th |                |               | 2N is HIGH. |

| 11     | MDT      | lp               | Attenuator se  | erial data inpu                                                                    | ut                               |                                            |                |               | •           |

| 12     | MCK      | lp               | Attenuator bi  | it clock input                                                                     |                                  |                                            |                |               |             |

| 13     | MLEN     | lp               | Attenuator la  | tch enable in                                                                      | put                              |                                            |                |               |             |

| 14     | RSTN     | lp               | System rese    | t. Reset opera                                                                     | ation when LO                    | W, and normal ope                          | ration when H  | IIGH.         | •           |

| 15     | MUTE     | lp               | Mute control   | signal. Mutin                                                                      | g when HIGH,                     | and normal operati                         | ion when LO\   | N.            |             |

| 16     | DEMP     | lp               | Deemphasis     | control signa                                                                      | al. OFF when L                   | .OW, and ON when                           | HIGH.          |               |             |

|        |          |                  | Deemphasis     | filter select in                                                                   | nputs                            |                                            |                |               | •           |

| 17     | FSEL1    | lp               |                | FSEL1                                                                              |                                  | FSEL2                                      | Sa             | mpling frequ  | uency (fs)  |

|        |          |                  |                | LOW                                                                                |                                  | LOW                                        |                | 44.1 kH       | iz          |

|        | 1        |                  |                | LOW                                                                                |                                  | HIGH                                       |                | 48 kH:        | <u>.</u>    |

| 18     | FSEL2    | lp               |                | HIGH                                                                               | ~                                | LOW                                        |                | Test mo       | de          |

|        |          |                  |                | HIGH                                                                               |                                  | HIGH                                       |                | 32 kHz        | ζ           |

| 19     | OW20N    | lp               | Output bit ler | Output bit length select pin. 20-bit output when LOW, and 18-bit output when HIGH. |                                  |                                            |                |               |             |

| 20     | SYNCN    | lp               | Sync mode s    | select pin. No                                                                     | rmal sync mod                    | de when LOW, and j                         | itter-free mod | de when HIGI  | ١.          |

| 21     | TMOD1    | lp               | Dither proces  | ssing control.                                                                     | ON when LO                       | N, and OFF when H                          | IIGH.          |               |             |

| 22     | VDD      | -                | 5 V supply     |                                                                                    |                                  |                                            |                |               | •           |

# SM5843A×1

| Number | Name  | I/O <sup>1</sup> | Description                                                                                                       |

|--------|-------|------------------|-------------------------------------------------------------------------------------------------------------------|

| 23     | DOR   | 0                | Right-channel data output                                                                                         |

| 24     | DOL   | 0                | Left-channel data output                                                                                          |

| 25     | wcko  | 0                | Output word clock                                                                                                 |

| 26     | вско  | 0                | Output bit clock                                                                                                  |

| 27     | TMOD2 | lp               | Filter characteristic select pin. Sharp roll-off (response 1) when HIGH, and slow roll-off (response 2) when LOW. |

| 28     | LRCI  | lp               | Input data sample rate (fs) clock                                                                                 |

<sup>1.</sup> I = input, Ip = Input with pull-up resistor, O = output

## **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$V_{SS}=0\,V$

| Parameter                 | Symbol           | Rating                        | Unit  |

|---------------------------|------------------|-------------------------------|-------|

| Supply voltage range      | V <sub>DD</sub>  | -0.3 to 7.0                   | V     |

| Input voltage range       | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V     |

| Storage temperature range | T <sub>stg</sub> | -40 to 125                    | °C    |

| Power dissipation         | P <sub>D</sub> - | 550 (DIP)                     | mW    |

| i ower dissipation        |                  | 390 (SOP)                     | IIIVV |

| Soldering temperature     | T <sub>sld</sub> | 255                           | °C    |

| Soldering time            | t <sub>sld</sub> | 10                            | S     |

# **Recommended Operating Conditions**

fs = 384fs (CKSLN = HIGH):  $V_{SS} = 0$  V

| Parameter                   | Symbol           | Rating     | Unit |

|-----------------------------|------------------|------------|------|

| Supply voltage range        | V <sub>DD</sub>  | 4.5 to 5.5 | V    |

| Operating temperature range | T <sub>opr</sub> | -20 to 80  | °C   |

fs = 256fs (CKSLN = LOW):  $V_{SS} = 0$  V

| Parameter                   | Symbol           | Rating       | Unit |

|-----------------------------|------------------|--------------|------|

| Supply voltage range        | V <sub>DD</sub>  | 4.75 to 5.25 | V    |

| Operating temperature range | T <sub>opr</sub> | -20 to 70    | °C   |

#### **DC Electrical Characteristics**

$V_{\mathrm{DD}} = 4.5$  to 5.5 V,  $V_{\mathrm{SS}} = 0$  V,  $T_{\mathrm{a}} = -20$  to 80 °C

| Parameter                              | Symbol            | Condition                  |                    | Rating   |                    |                  |  |

|----------------------------------------|-------------------|----------------------------|--------------------|----------|--------------------|------------------|--|

| raidilietei                            | Symbol            | Condition                  | min                | typ      | max                | Unit             |  |

| Current consumption                    | I <sub>DD</sub>   | $V_{DD} = 5.0 V^{1}$       | -                  | 50       | 65                 | mA               |  |

| XTI HIGH-level input voltage           | V <sub>IH1</sub>  |                            | 0.7V <sub>DD</sub> | -        | -                  | ٧                |  |

| XTI LOW-level input voltage            | V <sub>IL1</sub>  |                            | -                  | -        | 0.3V <sub>DD</sub> | V                |  |

| XTI AC-coupled input voltage           | V <sub>INAC</sub> |                            | 0.3V <sub>DD</sub> | -        | -                  | V <sub>p-p</sub> |  |

| HIGH-level input voltage <sup>2</sup>  | V <sub>IH2</sub>  |                            | 2.4                | <b>-</b> | -                  | V                |  |

| LOW-level input voltage <sup>2</sup>   | V <sub>IL2</sub>  |                            | -                  | -        | 0.5                | V                |  |

| HIGH-level output voltage <sup>3</sup> | V <sub>OH</sub>   | $I_{OH} = -0.4 \text{ mA}$ | 2.5                | -        |                    | ٧                |  |

| LOW-level output voltage <sup>3</sup>  | V <sub>OL</sub>   | I <sub>OL</sub> = 1.6 mA   | -                  | -        | 0.4                | ٧                |  |

| XTI HIGH-level input current           | I <sub>IH</sub>   | $V_{IN} = V_{DD}$          | -                  | 10       | 20                 | μА               |  |

| XTI LOW-level input current            | I <sub>IL1</sub>  | V <sub>IN</sub> = 0 V      | -                  | 10       | 20                 | μА               |  |

| LOW-level input current <sup>2</sup>   | I <sub>IL2</sub>  | V <sub>IN</sub> = 0 V      | -                  | 10       | 20                 | μА               |  |

| Input leakage current <sup>2</sup>     | I <sub>LH</sub>   | $V_{IN} = V_{DD}$          | -                  | -        | 1.0                | μА               |  |

<sup>1.</sup>  $f_{SYS} = 256fs = 14.2$  MHz (CKSLN = LOW), no output load 2. Pins DI/INF2N, BCKI, CKSLN, INF1N, IW1N/DIL, IW2N/DIR, MDT, MCK, MLEN, RSTN, MUTE, DEMP, FSEL1, FSEL2, OW20N, SYNCN, LRCI, TMOD1, TMOD2

<sup>3.</sup> Pins CKO, DOL, DOR, BCKO, WCKO

## **AC Electrical Characteristics**

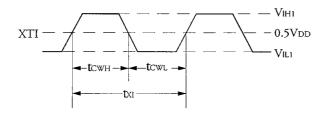

## Input Clock (XTI)

## **Crystal oscillator**

fs = 384fs (CKSLN = HIGH):  $V_{DD}$  = 4.5 to 5.5 V,  $V_{SS}$  = 0 V,  $T_a$  = -20 to 80 °C

| Parameter            | Symbol    |     | Unit |      |     |

|----------------------|-----------|-----|------|------|-----|

| i didiliotoi         |           | min | typ  | max  | Omt |

| Oscillator frequency | fosc fosc | 2.0 | -    | 21.2 | MHz |

fs = 256fs (CKSLN = LOW):

$$V_{DD}$$

= 4.75 to 5.25 V,  $V_{SS}$  = 0 V,  $T_a$  = -20 to 70 °C

| Parameter            | Symbol  | Rating |     | Unit |       |

|----------------------|---------|--------|-----|------|-------|

|                      | oyinbo: | min    | typ | max  | Ollit |

| Oscillator frequency | fosc    | 1.0    | _   | 14.2 | MHz   |

## **External clock input**

fs = 384fs (CKSLN = HIGH):  $V_{DD}$  = 4.5 to 5.5 V,  $V_{SS}$  = 0 V,  $T_a$  = -20 to 80 °C

| Parameter                   | Symbol           |     | Unit |     |      |

|-----------------------------|------------------|-----|------|-----|------|

|                             | Symbol           | min | typ  | max | Unit |

| Clock HIGH-level pulsewidth | tсwн             | 20  | -    | 250 | ns   |

| Clock LOW-level pulsewidth  | t <sub>CWL</sub> | 20  | -    | 250 | ns   |

| Clock pulse cycle time      | t <sub>XI</sub>  | 47  | -    | 500 | ns   |

fs = 256fs (CKSLN = LOW):

$$V_{DD}$$

= 4.75 to 5.25 V,  $V_{SS}$  = 0 V,  $T_a$  = -20 to 70 °C

| Parameter                   | Symbol           |     | Unit |      |      |

|-----------------------------|------------------|-----|------|------|------|

|                             | Symbol           | min | typ  | max  | Unit |

| Clock HIGH-level pulsewidth | <sup>‡</sup> CWH | 30  | -    | 500  | ns   |

| Clock LOW-level pulsewidth  | t <sub>CWL</sub> | 30  | -    | 500  | ns   |

| Clock pulse cycle time      | t <sub>XI</sub>  | 70  | -    | 1000 | ns   |

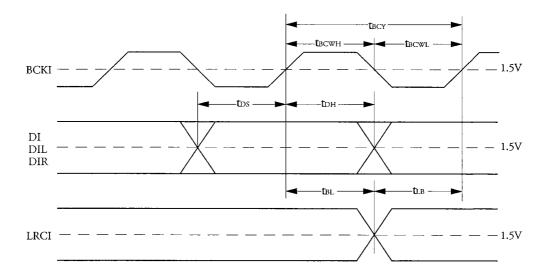

# Serial input timing (BCKI, DI, DIL, DIR, LRCI)

$$\rm V_{DD}$$

= 4.5 to 5.5 V,  $\rm V_{SS}$  = 0 V,  $\rm T_a$  = –20 to 80 °C

| Parameter                           | Symbol           |     | Unit |     |      |

|-------------------------------------|------------------|-----|------|-----|------|

|                                     | Symbol           | min | typ  | max | Onit |

| BCKI HIGH-level pulsewidth          | †BCWH            | 50  | -    | _   | ns   |

| BCKI LOW-level pulsewidth           | †BCWL            | 50  | -    | -   | ns   |

| BCKI pulse cycle                    | t <sub>BCY</sub> | 100 | -    |     | ns   |

| DIN setup time                      | t <sub>DS</sub>  | 50  | -    | -   | ns   |

| DIN hold time                       | t <sub>DH</sub>  | 50  | -    | -   | ns   |

| Last BCKI rising edge to LRCI edge  | t <sub>BL</sub>  | 50  | -    |     | ns   |

| LRCI edge to first BCKI rising edge | <b>t</b> ⊥в      | 50  | -    | _   | ns   |

# Reset timing (RSTN)

$$V_{DD} = 4.5$$

to 5.5 V,  $V_{SS} = 0$  V,  $T_a = -20$  to 80 °C

| Parameter                       | Symbol             | Symbol Condition   |     | Rating |     |      |

|---------------------------------|--------------------|--------------------|-----|--------|-----|------|

| Turumotor                       | - Cymbor Condition |                    | min | typ    | max | Unit |

| RST LOW-level reset pulsewidth  | t_ a_              | At power-ON        | 1   | _      | _   | μs   |

| 1101 LOTT IOVOITOSEL PUISEWIUIT | <sup>I</sup> RST   | At all other times | 50  | _      | _   | ns   |

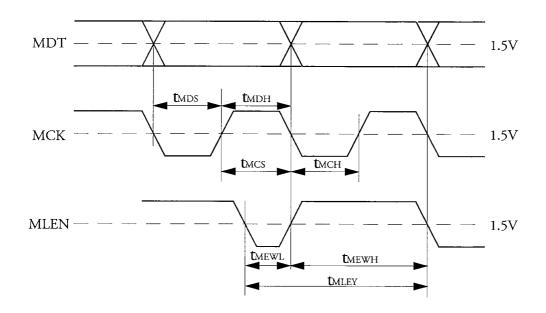

# Attenuator timing (MDT, MCK, MLEN)

$V_{\mathrm{DD}}$  = 4.5 to 5.5 V,  $V_{\mathrm{SS}}$  = 0 V,  $T_{\mathrm{a}}$  = -20 to 80 °C

| Parameter                  | Symbol             |     | Rating | l l'mit |                    |

|----------------------------|--------------------|-----|--------|---------|--------------------|

|                            | Symbol             | min | typ    | max     | Unit               |

| MDT setup time             | t <sub>MDS</sub>   | 20  | _      | -       | ns                 |

| MDT hold time              | t <sub>M</sub> DH  | 20  | -      | -       | ns                 |

| MLEN setup time            | twcs               | 40  | -      | -       | ns                 |

| MLEN hold time             | t <sub>M</sub> CH  | 20  | _      | _       | ns                 |

| MLEN LOW-level pulsewidth  | <sup>†</sup> MEWL  | 20  | _      | -       | ns                 |

| MLEN HIGH-level pulsewidth | t <sub>MEWH</sub>  | 20  | -      | -       | ns                 |

| MLEN pulse cycle time      | t <sub>M</sub> LEY | 6   | -      | -       | t <sub>SYS</sub> 1 |

<sup>1.</sup>  $t_{SYS} = 1/384 fs$  when CKSLN is HIGH, and 1/256 fs when CKSLN is LOW.

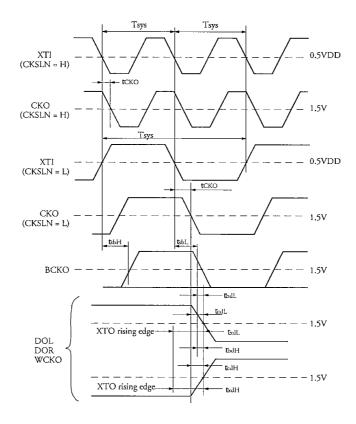

# **Output timing**

$\rm V_{DD}$  = 4.5 to 5.5 V,  $\rm V_{SS}$  = 0 V,  $\rm T_a$  = –20 to 80 °C,  $\rm C_L$  = 15 pF

| Parameter                          | Symbol           | Condition                |         | Rating |     | Unit |  |

|------------------------------------|------------------|--------------------------|---------|--------|-----|------|--|

| raidilletei                        | Symbol           | Condition                | min typ |        | max | Unit |  |

| XTI to XTO delay                   | tхто             | XTI fall to XTO rise     | 3       | -      | 15  | ns   |  |

| XTI to CKO delay                   | tско             | XTI fall to CKO fall     | 10      | _      | 35  | ns   |  |

| VTI to DOVO dolov /OVOLNI - LIIOU) | t <sub>sbH</sub> | XTI fall to BCKO rise    | 20      | -      | 60  |      |  |

| XTI to BCKO delay (CKSLN = HIGH)   | t <sub>sbL</sub> | XTI fall to BCKO fall    | 20      | _      | 60  | ns   |  |

| XTI to BCKO delay (CKSLN = LOW)    | t <sub>sbH</sub> | XTI fall to BCKO rise    | 20      | -      | 60  | ns   |  |

|                                    | t <sub>sbL</sub> | XTI fall to BCKO fall    | 20      | _      | 60  |      |  |

| POKO to DOL. DOD. MCKO dolov       | t <sub>bdH</sub> | BCKO fall to output rise | 5       | -      | 10  |      |  |

| BCKO to DOL, DOR, WCKO delay       | t <sub>bdL</sub> | BCKO fall to output fall | -5      | -      | 10  | - ns |  |

| CKO TODOL DOD WCKO dolov           | t <sub>cdH</sub> | CKO fall to output rise  | 5       | _      | 25  | †    |  |

| CKO TODOL, DOR, WCKO delay         | t <sub>cdL</sub> | CKO fall to output fall  | 5       | -      | 25  | ns   |  |

| VTO TODOL DOD WCKO dalaw           | t <sub>xdH</sub> | XTO rise to output rise  | 15      | _      | 50  |      |  |

| XTO TODOL, DOR, WCKO delay         | t <sub>xdL</sub> | XTO rise to output fall  | 15      | _      | 50  | ns   |  |

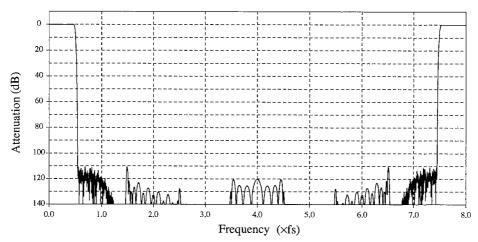

## **Filter Characteristics**

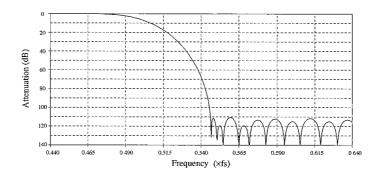

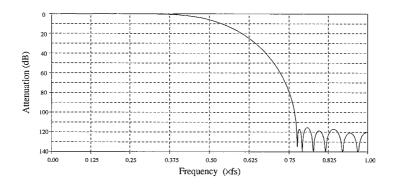

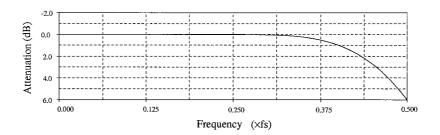

# 8-times interpolation filter (sharp roll-off: response 1)

| Parameter                | Condition    | Rating @ 256fs       |

|--------------------------|--------------|----------------------|

| Passband                 |              | 0 to 0.4535fs        |

| Stopband                 |              | 0.5465fs to 7.4535fs |

| Passband ripple          |              | ≤±0.00005 dB         |

| Stopband attenuation     |              | ≥ 110 dB             |

| Orang dalari             | SYNCN = LOW  | 44.625/fs            |

| Group delay <sup>1</sup> | SYNCN = HIGH | 44.25/fs to 45.0/fs  |

<sup>1.</sup> The digital filter arithmetic computation time from when the completion of data input at rate fs to the start of data output at rate 8fs.

## 8fs filter response with deemphasis OFF

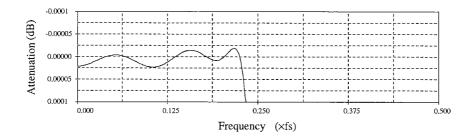

#### 8fs filter band transition response with deemphasis OFF

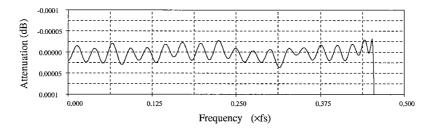

# 8fs filter passband response with deemphasis OFF

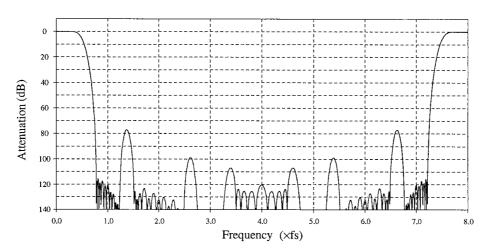

# 8-times interpolation filter (slow roll-off: response 2)

| Parameter                | Condition           | Rating @ 256fs      |

|--------------------------|---------------------|---------------------|

| Passband                 | < 3 dB attenuation  | 0 to 0.455fs        |

| Stopband                 | > 77 dB attenuation | 0.745fs to 7.255fs  |

| Passband ripple          | 0 to 0.235fs        | ≤±0.00003 dB        |

| Stopband attenuation     |                     | ≥ 77 dB             |

| Overing delevil          | SYNCN = LOW         | 25.625/fs           |

| Group delay <sup>1</sup> | SYNCN = HIGH        | 25.25/fs to 26.0/fs |

<sup>1.</sup> The digital filter arithmetic computation time from when the completion of data input at rate fs to the start of data output at rate 8fs.

## 8fs filter response with deemphasis OFF

## 8fs filter band transition response with deemphasis OFF

## 8fs filter passband response with deemphasis OFF

## 8fs filter passband response [amplitude gain enlarged]

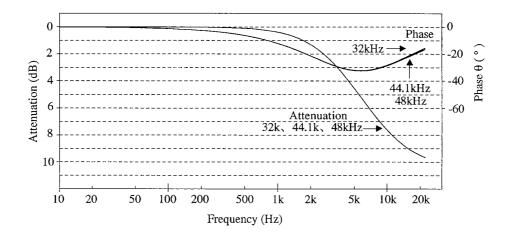

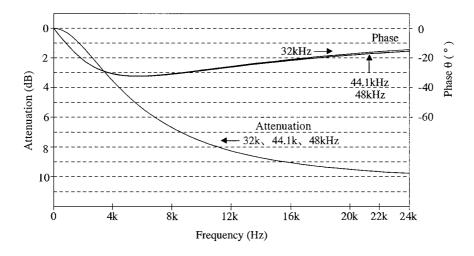

## Deemphasis filter

| Pore                                 | motor       | Sampling frequency (fs) |            |                                       |  |

|--------------------------------------|-------------|-------------------------|------------|---------------------------------------|--|

| Parameter                            |             | 32 kHz                  | 44.1 kHz   | 48 kHz                                |  |

| Passband bandwidth (kHz)             |             | 0 to 14.5               | 0 to 20.0  | 0 to 21.7                             |  |

| Deviation from ideal above at wintin | Attenuation |                         | ≤±0.001 dB | · · · · · · · · · · · · · · · · · · · |  |

| Deviation from ideal characteristic  | Phase, θ    | 0 to 1.5°               |            |                                       |  |

## Passband response with deemphasis ON (logarithmic frequency axis)

## Passband response with deemphasis ON (linear frequency axis)

#### **FUNCTIONAL DESCRIPTION**

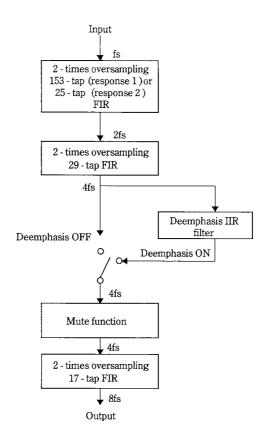

The basic arithmetic block is shown in figure 1, and the function of each block is described in the following sections.

Figure 1. Arithmetic block diagram

#### 8-times Oversampling (Interpolation)

The interpolation arithmetic block is comprised of 3 cascaded, 2-times FIR interpolation filters, as shown in figure 1.

The input signal is sampled at rate fs, and then 8-times oversampling data is output. Sampling noise in the 0.5465fs to 7.4535fs stopband for the sharp roll-off (response 1) characteristic, 0.745fs to 7.255fs for the slow roll-off (response 2) characteristic, is removed by the interpolation filter.

#### **Digital Deemphasis**

The digital deemphasis filter has the same construction as analog filters. It is implemented as an IIR filter to faithfully reproduce the gain and phase characteristics of standard analog deemphasis filters. The three sets of filter coefficients for the three fs = 32.0/44.1/48.0 kHz sampling frequencies are selected by FSEL1 and FSEL2 when the sampling frequency is specified, as shown in the following table. Deemphasis is ON when DEMP is HIGH, and OFF when DEMP is LOW.

| FSEL1 | FSEL2 | Sampling frequency (fs) |  |

|-------|-------|-------------------------|--|

| LOW   | LOW   | 44.1 kHz                |  |

| LOW   | HIGH  | 48 kHz                  |  |

| HIGH  | LOW   | Test mode               |  |

| HIGH  | HIGH  | 32 kHz                  |  |

Note that test mode is not available for operation.

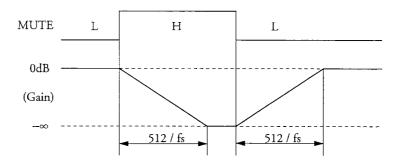

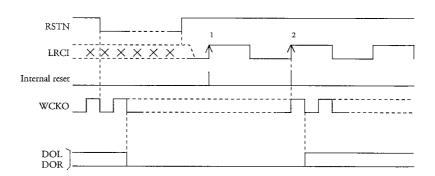

#### **Soft Muting**

The muting function controls the muting of both left and right channels simultaneously. Muting is ON when MUTE is HIGH, muting is OFF when MUTE is LOW. When MUTE goes HIGH, the attenuation changes smoothly from 0 to  $-\infty$  dB in 512/fs, or approximately 11.6 ms when fs = 44.1 kHz. When MUTE goes LOW, muting is released and the attenuation changes smoothly from  $-\infty$  to 0 dB, again taking approximately 11.6 ms.

Figure 2. Mute timing

When RSTN goes LOW, the DOL and DOR outputs go LOW, immediately muting the output signal.

Muting is released and timing is synchronized immediately after RSTN goes HIGH.

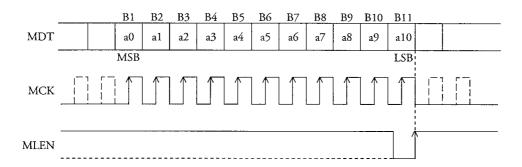

#### Digital Attenuator (MDT, MCK, MLEN)

The attenuation function is controlled by MDT, MCK and MLEN. MDT data, in 11-bit serial MSB first format, is shifted into an internal shift register on the rising edge of the serial data clock MCK. The

contents of the shift register are transferred to the internal processing circuits on the rising edge of the MLEN gate pulse. The attenuation data format is shown in figure 3.

Figure 3. Attenuation data format

The attenuation register data DATT can take on any value between 0 and 1024 (400<sub>H</sub>). The attenuation is given by the following equation for both left and right channels simultaneously.

Attenuation =  $20 \times \log_{10}(DATT/1024)$  [dB]

Thus, the attenuation level is  $-\infty$  when DATT is 0, and attenuation is 0 dB when DATT is 1024. DATT is set to 1024 (400<sub>H</sub>) after system reset initialization. The attenuation data and attenuation level for sample DATT values are shown in the following table.

| Attenuation data DATT                      | Attenuation level (dB)   |

|--------------------------------------------|--------------------------|

| 000 <sub>H</sub>                           | -∞                       |

| 001 <sub>H</sub><br>to<br>3FF <sub>H</sub> | -60.206<br>to<br>-0.0085 |

| 400 <sub>H</sub>                           | 0                        |

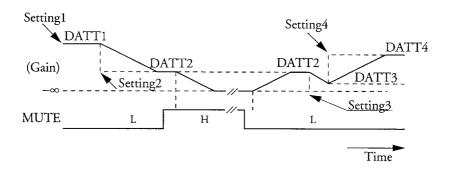

#### Attenuation operation

When an attenuation value DATT is set, the attenuation changes smoothly from the current attenuation level to the new level. The new attenuation data is stored in the attenuation register while the current attenuation data is stored in a temporary register. The attenuation then changes smoothly by ramping between the two register values, updating the temporary register with each step. If a new attenuation

value for DATT is set before the previous target attenuation level is reached, the attenuation then ramps toward the new attenuation level.

When MUTE is HIGH, the attenuation level is  $-\infty$ . When MUTE goes LOW (muting OFF), the attenuation level returns to that of the original value of DATT.

Figure 4. Attenuation and mute timing

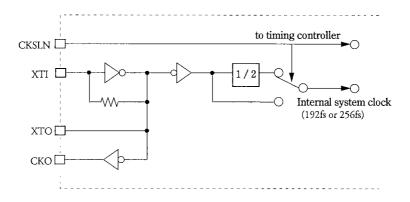

#### System Clock (XTI, XTO, CKO, CKSLN)

Two system clock frequencies, 384fs and 256fs, can be used. An external clock source can be input on XTI, or a crystal oscillator can be constructed by connecting a crystal between XTI and XTO. The system clock is also buffered and then output on CKO. The system clock frequency selection and the internal clock frequency are shown in the following table.

| Parameter                                       | CKSL              |                 |  |

|-------------------------------------------------|-------------------|-----------------|--|

| raidiletei                                      | HIGH              | LOW             |  |

| XTI input clock frequency $(f_{XI} = 1/t_{XI})$ | 384fs             | 256fs           |  |

| CKO clock frequency                             | 384fs             | 256fs           |  |

| Internal clock frequency (t <sub>SYS</sub> )    | $2 \times t_{XI}$ | t <sub>XI</sub> |  |

Figure 5. Clock generator circuit

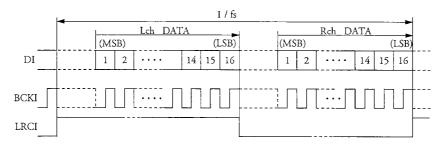

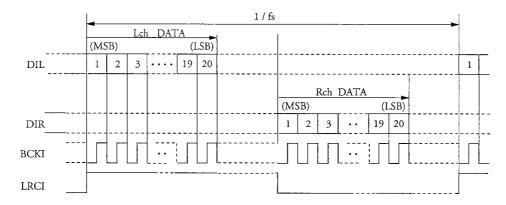

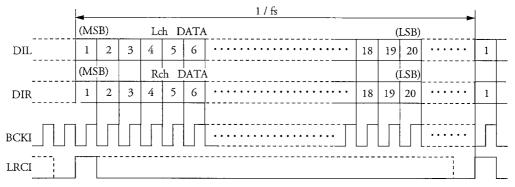

# Audio Data Input (INF1N, INF2N, IW1N, IW2N, DI, DIL, DIR, BCKI, LRCI)

The input data format and several input pin functions are selected by the state of INF1N and INF2N.

| INEAN   | INF1N DI/INF2N | lanut format                                | Pin function selection |          |           |

|---------|----------------|---------------------------------------------|------------------------|----------|-----------|

| IMP III | DI/INFZIN      | Input format                                | DI/INF2N               | IW1N/DIL | IW2N/DIR  |

| LOW     | LOW            | LD allowed to the date                      |                        | BUZN     | NA COLUMN |

| LOW     | HIGH           | LR alternating <sup>1</sup> , trailing data | DI                     | IW1N     | IW2N      |

| HIGH    | LOW            | LR alternating, leading data                |                        | 212      |           |

| HIGH    | HIGH           | LR simultaneous <sup>2</sup> , leading data | INF2N                  | DIL      | DIR       |

- 1. Alternating left-channel and right-channel data input on a single input DI.

- 2. Simultaneous left-channel and right-channel data input on two inputs, DIL and DIR, respectively.

The input data word length is selected by the state of IW1N and IW2N when INF1N is LOW. 20-bit is selected when INF1N is HIGH.

| INF1N | IW2N/DIL | IW1N/DIR | Input bit length |

|-------|----------|----------|------------------|

|       | LOW      | LOW      | 20 bits          |

| LOW   | LOW      | HIGH     | 20 bits          |

| LOW   | HIGH     | LOW      | 18 bits          |

|       | HIGH     | HIGH     | 16 bits          |

| HIGH  | ×        | ×        | 20 bits          |

#### **Jitter-free Function (SYNCN)**

The arithmetic circuit and output control timing is derived from the system clock, and is therefore independent of the input LRCI and BCKI clocks. Accordingly, any jitter in the data input clock (LRCI and BCKI) does not cause jitter in the output.

Generally, the internal timing is synchronized to the LRCI input timing after a system reset release, when RSTN goes from LOW to HIGH, on the first LRCI clock start edge. If the input timing and LRCI start edge timing subsequently drift, the input timing is automatically resynchronized when the timing error

exceeds a certain value. There are 2 timing error values at which resynchronization occurs, selected by the state of SYNCN.

#### Jitter-free mode (SYNCN = HIGH)

When SYNCN is HIGH, the timing error value is  $\pm 3/8 \times (LRCI \ clock \ period)$ . When the difference between the input timing and LRCI start edge position do not exceed this value, internal timing is not resynchronized and all functions continue to operate normally.

#### Sync mode (SYNCN = LOW)

When SYNCN is LOW, the timing error value is  $\pm 1 \times$  (system clock period), which is a much smaller timing error tolerance than in jitter-free mode. In this mode, the internal timing is guaranteed to follow the LRCI clock timing within this tolerance, making this mode useful for systems constructed from a multiple number of SM5843A×1 devices.

Note that resynchronization affects the internal operation and can generate a momentary click noise output.

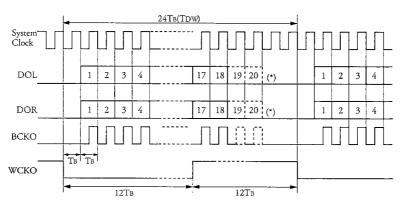

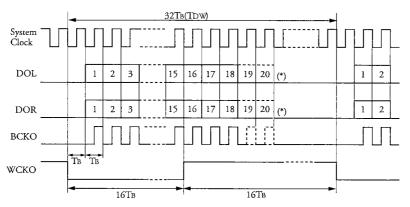

#### Audio Data Output (DOL, DOR, BCKO, WCKO, OW20N)

The output data is in serial, simultaneous left and right-channel, 2s complement, MSB first, BCKO burst (NPC format) format. The output data word length is selected by the state of OW20N. 18-bit output is selected when OW20N is HIGH, and 20-bit output when OW20N is LOW.

8fs serial data is output in sync with the falling edge of the internal system clock and BCKO clock. The number of BCKO bit clock pulses per word changes depending on the output bit length selected (18/20 bits). Consequently, output data is latched into the internal output register on the falling of the edge of an output word clock WCKO, which has timing

independent of the number of output bits as specified in the following table.

| Parameter        | Symbol          | CKSLN = HIGH       | CKSLN = LOW        |

|------------------|-----------------|--------------------|--------------------|

| Bit clock rate   | T <sub>B</sub>  | 1/192fs            | 1/256fs            |

| Data word length | T <sub>DW</sub> | 24t <sub>SYS</sub> | 32t <sub>SYS</sub> |

## System Reset (RSTN)

The SM5843A×1 must be reset under the following conditions.

- At power-ON.

- When the LRCI clock and internal operation timing need to be resynchronized.

- When switching the CKSLN clock select input.

- When switching between filter characteristics using TMOD2.

- When either or both of the LRCI and XTI clocks stop or are interrupted.

The system is reset by applying a LOW-level pulse on RSTN.

The arithmetic and output timing counters are reset on the first LRCI start edge after reset is released, as long as the XTI clock has already stabilized. The LRCI start edge is determined by the state of INF1N and INF2N. When INF1N is LOW or when both INF1N and INF2N are HIGH, the start edge is the rising edge. When INF1N is HIGH and INF2N is LOW, the start edge is the falling edge.

When RSTN is LOW, the DOL and DOR outputs are LOW, muting the output signal to an attenuation level of  $-\infty$ .

The power-ON reset pulse can be applied by a microcontroller or, for systems where XTI and LRCI are stable at power-ON, by connecting a capacitor of several hundred pF between RSTN and VSS. For systems that do not use a microcontroller, the capacitor must be chosen such that the XTI and LRCI clocks fully stabilize before RSTN goes from LOW to HIGH.

Figure 6. System reset timing and output muting

#### Filter Characteristic Selection (TMOD2)

There are 2 digital filter frequency response characteristics incorporated into the SM5843A×1, selected by the state of TMOD2. A sharp roll-off characteristic (response 1) is selected when TMOD2 is HIGH, and a slow roll-off characteristic (response 2) when TMOD2 is LOW. The response is modified by changing the number of taps in the 1st FIR filter stage, as shown in figure 1.

- Filter response 1

- 153-tap 1st FIR

- 29-tap 2nd FIR

- 17-tap 3rd FIR

- Filter response 2

- 25-tap 1st FIR

- 29-tap 2nd FIR

- 17-tap 3rd FIR

Note that the device should be reset when changing TMOD2 during normal operation.

# Dither Rounding-off Processing (TMOD1)

Dither rounding-off processing of output data is ON when TMOD1 is LOW. Dither is OFF and normal processing mode is selected when TMOD1 is HIGH.

## **TIMING DIAGRAMS**

# Input Timing Examples (DIN, BCKI, LRCI)

Figure 7. LR alternating, trailing data, 16-bit input

Data after lsb (bit 20) is ignored. After bit 20, BCKI clock input is not needed. Figure 8. LR alternating, leading data, 20-bit input

Data after lsb (bit20) is ignored. After bit 20, BCKI clock input is not needed. Figure 9. LR simultaneous, leading data, 20-bit input

# Output Timing Examples (DOL, DOR, BCKO, WCKO)

The number of output bits is determined by the output bit length selected.

Figure 10. 18/20-bit output ( $\overline{CKSL} = HIGH$ )

The number of output bits is determined by the output bit length selected.

Figure 11. 18/20-bit output ( $\overline{CKSL} = LOW$ )

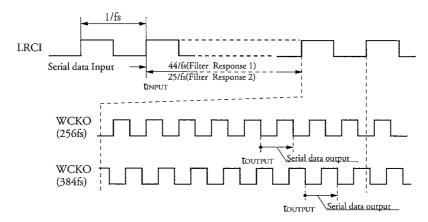

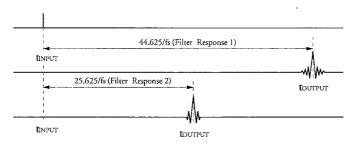

# **Data Input to Output Delay Timing**

This is the digital filter arithmetic computation time from the completion of data input at rate fs  $(t_{\mbox{\footnotesize{INPUT}}})$

on the rising edge of LRCI to the start of data output at rate  $8 \text{fs} \ (t_{OUTPUT})$  on the falling edge of WCKO.

| Filter response   | CKSLN        | SYNCN | Mode                    | toutput - tinput      |

|-------------------|--------------|-------|-------------------------|-----------------------|

| Filter response 1 | LOW (256fs)  | LOW   | After reset + sync mode | 44.625/fs             |

|                   |              | HIGH  | Jitter-free mode        | 44.25/fs - 45.0/fs    |

|                   | HIGH (384fs) | LOW   | After reset + sync mode | 44.75/fs              |

|                   |              | HIGH  | Jitter-free mode        | 44.375/fs - 45.125/fs |

| Filter response 2 | LOW (256fs)  | LOW   | After reset + sync mode | 25.625/fs             |

|                   |              | HIGH  | Jitter-free mode        | 25.25/fs - 26.0/fs    |

|                   | HIGH (384fs) | LOW   | After reset + sync mode | 25.75/fs              |

|                   |              | HIGH  | Jitter-free mode        | 25.375/fs - 26.125/fs |

Figure 12. Delay timing (SYNCN = LOW)

Figure 13. Delay timing (SYNCN = CKSLN = LOW)

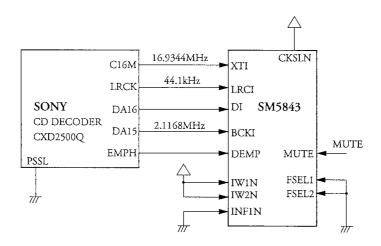

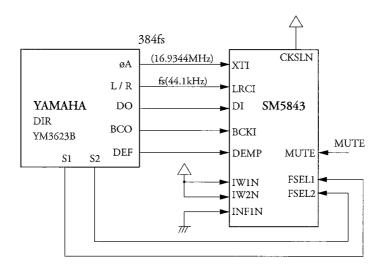

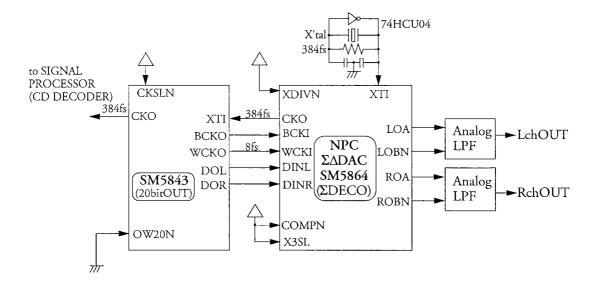

## **APPLICATION CIRCUITS**

# **Input Interface Circuits**

# CD decoder (CXD2500Q) connection

# Digital audio interface receiver (YM3623B) connection

## **Output Interface Circuits**

## 20-bit input $\Sigma\Delta$ DAC (SM5864AP) connection 1

## 20-bit input $\Sigma\Delta$ DAC (SM5864AP) connection 2

#### L/R-channel independent complementary PWM output