D F 1700

# Dual Channel, 8x Oversampling DIGITAL FILTER

### **FEATURES**

- DUAL CHANNEL DIGITAL

INTERPOLATION FILTERS

- ACCEPTS 16-BIT INPUT DATA

- USER-SELECTABLE FOR 16-,18-, OR 20-BIT OUTPUT DATA

- SERIAL OUTPUT IS COMPATIBLE WITH PCM1700 AND PCM63 DACs

- PASSBAND RIPPLE < 0.00005dB

- STOPBAND ATTENUATION > 110dB

- SINGLE +5V POWER SUPPLY FOR LOW POWER DISSIPATION OF 250mW Max

- PLASTIC 28-PIN DIP AND 40-PIN SOIC PACKAGES

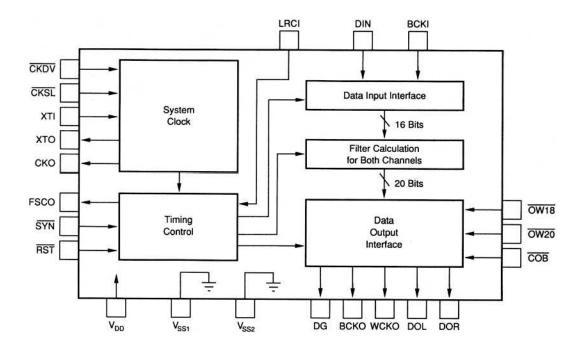

## DESCRIPTION

The DF1700 is a high performance, 8x oversampling CMOS digital filter. This filter accepts 16-bit input data and is user-selectable for 16-, 18-, or 20-bit output data. The 8x oversampling feature converts the input data frequency (fs) to an output data frequency of 8 x fs by digital interpolation. By providing 8x oversampled data to an audio DAC, lower order analog filters can be used at the DAC's output, thus reducing filter phase non-linearities. Oversampling with the DF1700 simultaneously improves the fidelity of the analog reconstruction and reduces analog filter complexity at the output of the DAC.

The DF1700 is available in a plastic 28-pin DIP and a 40-pin SOIC package, and is designed for compatibility with the Burr-Brown PCM1700 and PCM63 digitalto-analog converters.

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (602) 746.1111 • Twx: 910. 952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (602) 889.1510 • Immediate Product Info: (800) 548-6132

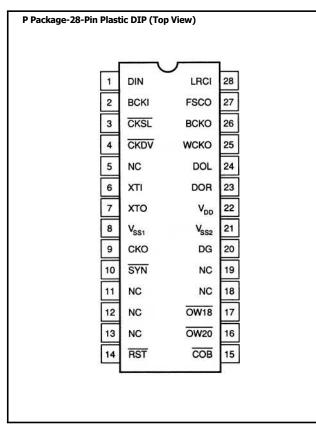

### **PIN CONFIGURATION**

| U Package-40-Pin Pl | astic SOIC (T    | op View)         |    |

|---------------------|------------------|------------------|----|

| 1                   | NC ●             | V <sub>SS1</sub> | 40 |

| 2                   | NC               | хто              | 39 |

| 3                   | NC               | XTI              | 38 |

| 4                   | ско              | CKDV             | 37 |

| 5                   | NC               | NC               | 36 |

| 6                   | NC               | NC               | 35 |

| 7                   | SYN              | CKSL             | 34 |

| 8                   | NC               | BCKI             | 33 |

| 9                   | NC               | DIN              | 32 |

| 10                  | NC               | NC               | 31 |

| 11                  | RST              | LRCI             | 30 |

| 12                  | COB              | FSCO             | 29 |

| 13                  | OW20             | вско             | 28 |

| 14                  | OW18             | WCKO             | 27 |

| 15                  | NC               | NC               | 26 |

| 16                  | NC               | DOL              | 25 |

| 17                  | NC               | NC               | 24 |

| 18                  | DG               | DOR              | 23 |

| 19                  | NC               | NC               | 22 |

| 20                  | V <sub>SS2</sub> | V <sub>DD</sub>  | 21 |

|                     |                  |                  |    |

### **PIN DESCRIPTION**

| PIN NUI | MBER |                  |                         |                                                                     |

|---------|------|------------------|-------------------------|---------------------------------------------------------------------|

| SOIC    | DIP  | NAME             | 1/0(1)                  | DESCRIPTION                                                         |

| 1       | -    | NC               | -                       |                                                                     |

| 2       | -    | NC               | -                       |                                                                     |

| 3       | -    | NC               | _                       |                                                                     |

| 4       | 9    | СКО              | 0                       | Clock output (same frequency as XTI                                 |

|         |      |                  |                         | input clock).                                                       |

| 5       | -    | NC               | -                       |                                                                     |

| 6       | 1220 | NC               | - 22                    |                                                                     |

| 7       | 10   | SYN              | 1                       | H: Free-running mode;                                               |

|         |      | 20               |                         | L: Forced synchronizing mode.                                       |

| 8       | 11   | NC               |                         |                                                                     |

| 9       | 12   | NC               | -                       |                                                                     |

| 10      | 13   | NC               |                         |                                                                     |

| 11      | 14   | RST              | - 1                     | H: Normal operation; L: System reset.                               |

| 12      | 15   | COB              | 1                       | Select output data format-                                          |

|         |      |                  |                         | H: Two's complement;                                                |

| 192     | 1.2  |                  | 10                      | L: Complemented offset binary (COB).                                |

| 13      | 16   | OW20             |                         | Select number of output data bits. <sup>(2)</sup>                   |

| 14      | 17   | OW18             | 1                       | Select number of output data bits. <sup>(2)</sup>                   |

| 15      | _    | NC               | -                       |                                                                     |

| 16      | 18   | NC               | -                       |                                                                     |

| 17      | 19   | NC               | -                       |                                                                     |

| 18      | 20   | DG               | 0                       | Deglitch control clock.                                             |

| 19      | -    | NC               | -                       |                                                                     |

| 20      | 21   | V <sub>SS2</sub> | -                       | Ground 2.                                                           |

| 21      | 22   | VDD              | 1.000                   | Supply voltage (+5V).                                               |

| 22      | -    | NC               | -                       |                                                                     |

| 23      | 23   | DOR              | 0                       | Rch serial data output (8fs rate).                                  |

| 24      | -    | NC               | ō                       | Laboration data and and (Ole reste)                                 |

| 25      | 24   | DOL              | 0                       | Lch serial data output (8fs rate).                                  |

| 26      | -    | NC               | -                       |                                                                     |

| 27      | 25   | WCKO             | 0                       | Output timing control (word clock).                                 |

| 28      | 26   | вско             | 0                       | Output timing control for serial data                               |

|         | 07   | FSCO             |                         | (bit clock).                                                        |

| 29      | 27   |                  | 0                       | Internal timing clock (fs rate)                                     |

| 30      | 28   | LRCI             | E.                      | Multiplex clock for Lch/Rch input data<br>(fs rate)—H: Lch; L: Rch. |

| 31      |      | NC               |                         | (Is fale)                                                           |

| 32      | 1    | DIN              | ī                       | Serial data input.                                                  |

| 32      | 2    | BCKI             | l i                     | Timing clock for serial input data.                                 |

| 34      | 3    | CKSL             | L î                     | Select system clock. <sup>(2)</sup>                                 |

| 35      | 3    | NC               | 20 <b>9</b> 00<br>71220 | Select system clock.                                                |

| 36      | 5    | NC               |                         |                                                                     |

| 30      | 4    | CKDV             | ī                       | Select system clock.(2)                                             |

| 37      | 6    | XTI              |                         | Input for oscillator or external clock                              |

| 30      | 0    |                  |                         | (system clock).                                                     |

| 39      | 7    | хто              | 0                       | Output for oscillator; not connected                                |

| 00      |      | AIU AIU          | ľ                       | when using external clock.                                          |

| 40      | 8    | V <sub>ss1</sub> | -                       | Ground 1.                                                           |

|         |      | 551              | 1                       |                                                                     |

NOTES: (1) I = Input terminal; O = Output terminal. (2) Refer to the Functional Description section for details.

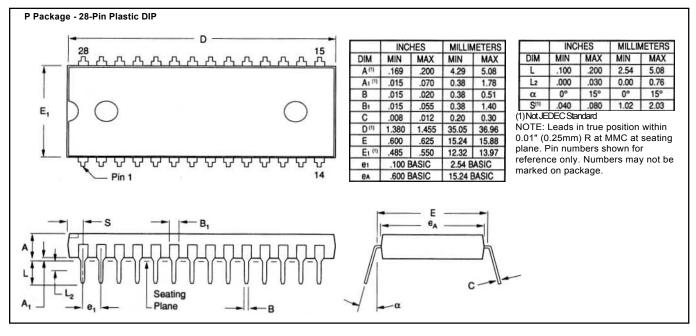

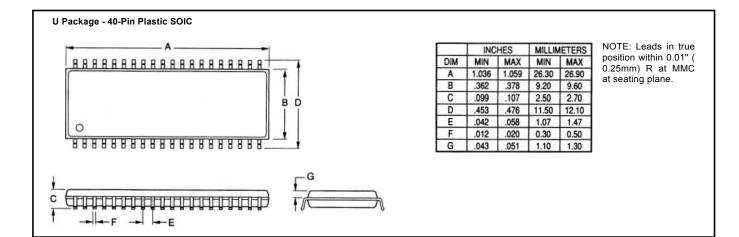

#### MECHANICAL

## DC SPECIFICATIONS

### ELECTRICAL

DIGITAL CHARACTERISTICS:  $V_{DD} = 4.75V$  to 5.25V,  $V_{ss} = 0V$ ,  $T_{A} = -20^{\circ}C$  to +70°C unless otherwise specified.

|                                 |     |                                                                              |                                                   |                    | DF1700P/U |                    |        |

|---------------------------------|-----|------------------------------------------------------------------------------|---------------------------------------------------|--------------------|-----------|--------------------|--------|

| PARAMETER                       | PIN | SYMBOL                                                                       | CONDITION                                         | MIN                | ТҮР       | MAX                | UNITS  |

| INPUT                           |     |                                                                              |                                                   |                    |           |                    |        |

| Logic Family                    |     |                                                                              |                                                   |                    | CMOS      |                    |        |

| Logic Voltages                  | XTI | V <sub>IL1</sub><br>V <sub>IH1</sub><br>V <sub>IL2</sub><br>V <sub>IH2</sub> |                                                   |                    |           | 0.3V <sub>DD</sub> |        |

|                                 | XTI | V <sub>1H1</sub>                                                             |                                                   | 0.7V <sub>DD</sub> |           |                    |        |

|                                 | (1) | V <sub>IL2</sub>                                                             |                                                   | 10.00              |           | 0.5                |        |

|                                 | (1) | V <sub>IH2</sub>                                                             |                                                   | 2.4                |           |                    |        |

| Input Leakage Current           | XTI | I <sub>LH</sub>                                                              | $V_{iN} = V_{DD}$                                 |                    | 10        | 20                 | μА     |

| 14 2450                         | XTI | · I <u>L</u>                                                                 | $V_{IN} = V_{DD}$ $V_{IN} = 0V$ $V_{IN} = V_{DD}$ |                    | 10        | 20                 | μА     |

|                                 | (1) | I <sub>LH</sub>                                                              | $V_{iN} = V_{DD}$                                 |                    |           | 1                  | μΑ     |

| Input Current                   | (1) | l <sub>it</sub>                                                              | $V_{iN} = 0V$                                     |                    | 10        | 20                 | μА     |

| OUTPUT                          |     |                                                                              |                                                   |                    |           |                    |        |

| Logic Family                    |     |                                                                              |                                                   |                    | CMOS      |                    |        |

| Logic Voltages                  | (2) | Vol                                                                          | I <sub>oL</sub> = 1.6mA                           |                    |           | 0.4                | v<br>v |

|                                 | (2) | V <sub>OH</sub>                                                              | I <sub>он</sub> = -0.4mA                          | 2.5                |           |                    | v      |

| POWER SUPPLY REQUIREMENTS       |     |                                                                              |                                                   |                    |           |                    |        |

| Supply Voltages                 |     | VDD                                                                          |                                                   | 4.75               | 5         | 5.25               | v      |

| Supply Current                  |     | I <sub>pp</sub>                                                              | $V_{DD} = 5V, F_{SYS}^{(3)}$                      |                    |           | 45                 | mA     |

| Power Dissipation               | (   | P <sub>D</sub>                                                               | Nominal V <sub>DD</sub>                           |                    |           | 250                | mW     |

| TEMPERATURE RANGE (Ambient, T_) |     |                                                                              |                                                   |                    |           |                    |        |

| Specification                   |     |                                                                              |                                                   | -20                |           | 70                 | °C     |

| Operating                       |     |                                                                              |                                                   | -20                |           | 70                 | °C     |

NOTES: (1) Refers to pins LRCI, DIN, BCKI,  $\overrightarrow{CKSL}$ ,  $\overrightarrow{CKDV}$ ,  $\overrightarrow{SYN}$ ,  $\overrightarrow{RST}$ ,  $\overrightarrow{COB}$ ,  $\overrightarrow{OW20}$ , and  $\overrightarrow{OW18}$ . (2) Refers to pins CKO, DG, DOL, DOR, WCKO, BCKO, and FSCO. (3)  $F_{sys}$  is the frequency of the internal system clock.  $F_{sys} = F_{xt1}$  with  $\overrightarrow{CKDV} = H$  and  $F_{sys} = F_{xt1}/2$  with  $\overrightarrow{CKDV} = L$ .

## **AC SPECIFICATIONS**

### ELECTRICAL

$V^{}_{\rm DD}$  = 4.75V to 5.25V,  $V^{}_{\rm SS}$  = 0V,  $T^{}_{\rm A}$  = –20°C to 70°C unless otherwise specified.

|                       |                  | C    | ONDITIO | NC      | D   | F1700P | /U   |       | Timing W            | aveform |

|-----------------------|------------------|------|---------|---------|-----|--------|------|-------|---------------------|---------|

| PARAMETER             | SYMB             | CKSL | CKDV    | x fs(1) | MIN | ТҮР    | MAX  | UNITS |                     |         |

| XTI TERMINAL          |                  |      |         |         |     |        |      |       |                     |         |

| CRYSTAL OSCILLATOR    |                  |      |         |         |     |        |      |       | хті /               | 7       |

| Oscillating Frequency | f <sub>MAX</sub> | н    | н       | 192     | 1   |        | 13   | MHz   |                     |         |

|                       | f <sub>MAX</sub> | н    | L       | 384     | 2   |        | 26   | MHz   |                     |         |

|                       | f <sub>MAX</sub> | L    | н       | 256     | 1   |        | 13   | MHz   |                     |         |

|                       | f <sub>MAX</sub> | L    | L       | 512     | 2   |        | 26   | MHz   |                     |         |

| EXTERNAL CLOCK        |                  |      |         |         |     |        |      |       |                     |         |

| Clock Pulse Width     | t <sub>cw</sub>  | н    | н       | 192     | 35  |        | 500  | ns    |                     |         |

|                       | t <sub>cw</sub>  | н    | L       | 384     | 15  |        | 250  | ns    | - t <sub>cw</sub> - |         |

|                       | t <sub>cw</sub>  | L    | н       | 256     | 35  |        | 500  | ns    | C.                  |         |

|                       | t <sub>cw</sub>  | L    | L       | 512     | 15  |        | 250  | ns    |                     |         |

| Clock Period          | t <sub>cy</sub>  | н    | н       | 192     | 76  |        | 1000 | ns    |                     |         |

|                       | t <sub>cy</sub>  | н    | L       | 384     | 38  |        | 500  | ns    |                     |         |

|                       | t <sub>cy</sub>  | L    | н       | 256     | 76  |        | 1000 | ns    |                     |         |

|                       | t <sub>cy</sub>  | L    | L       | 512     | 38  |        | 500  | ns    |                     |         |

NOTES: (1) fs = sampling frequency.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

# AC SPECIFICATIONS (CONT)

### ELECTRICAL

$V_{DD}$  = 4.75V to 5.25V,  $V_{ss}$  = 0V,  $T_{A}$  = -20°C to 70°C unless otherwise specified.

|                                               |                 | D   | F1700P | /U  |       | Timing Waveform |

|-----------------------------------------------|-----------------|-----|--------|-----|-------|-----------------|

| PARAMETER                                     | SYMBOL          | MIN | TYP    | MAX | UNITS |                 |

| INPUT TIMING (BCKI, DIN, LRCI,                | xTI)            |     |        |     |       |                 |

| BCKI, Pulse Width                             | tecw            | 100 |        |     | ns    |                 |

| BCKI, Cycle Time                              | tacy            | 200 |        |     | ns    |                 |

| DIN, Setup Time                               | t <sub>os</sub> | 75  |        |     | ns    |                 |

| DIN, Hold Time                                | t <sub>DH</sub> | 75  |        |     | ns    | DIN X 1.5       |

| Rising Edge of Last<br>BCKI To Edge of LRCI   | t <sub>BL</sub> | 75  |        |     | ns    |                 |

| Edge of LRCI To Rising<br>Edge of First BCKI  | t.e             | 75  |        |     | ns    | LRCI 1.5        |

| Falling Edge of XTI<br>To Rising Edge of LRCI | t <sub>xL</sub> | 20  |        |     | ns    |                 |

| Rising Edge of LRCI<br>To Falling Edge of XTI | t <sub>u</sub>  | 0   |        | -   | ns    |                 |

|                 |        |                       | D   | F1700P | /U  |       | Timing Waveform  |

|-----------------|--------|-----------------------|-----|--------|-----|-------|------------------|

| PARAMETER       | SYMBOL | CONDITION             | MIN | ТҮР    | MAX | UNITS |                  |

| OUTPUT TIMING   |        |                       |     | 1      |     |       |                  |

| BCKO Delay Time | txbH   | CKDV = L              | 35  |        | 120 | ns    |                  |

| from XTI        | txbL   | CKDV = L              | 35  |        | 120 | ns    | T <sub>SYS</sub> |

|                 | txbH   | CKDV = H              | 35  |        | 120 | ns    |                  |

|                 | txbL   | CKDV = H              | 35  | 0      | 120 | ns    |                  |

| Output Delay    | tbdL   | C <sub>L</sub> = 15pF | -10 | 0      | 10  | ns    |                  |

|                 | tbdH   | C_ = 15pF             | -10 | 0      | 10  | ns    |                  |

|                 | 1 1    |                       |     |        |     |       | ← tsbH ← tsbL    |

|                 | 1 1    |                       |     |        |     |       | txbH + txbL      |

|                 | 1 1    |                       |     |        |     |       |                  |

|                 | 1 1    |                       |     |        |     |       | вско 1.5V        |

|                 | 1 1    |                       |     |        |     |       |                  |

|                 | 1 1    |                       |     |        |     |       | tbdL             |

|                 | 1 1    |                       |     |        |     |       |                  |

|                 | 1 1    |                       |     |        |     |       | DOL              |

|                 | 1 1    |                       |     |        |     |       | DOR 1.5V         |

|                 | 1 1    |                       |     |        |     |       | DGL C            |

|                 | 1 1    |                       |     |        |     |       | DGR tbdH<br>WCKO |

|                 |        |                       |     |        |     |       |                  |

|                 |        |                       |     |        |     |       | 1.5V             |

|                 |        |                       |     |        |     |       |                  |

#### **ORDERING INFORMATION**

|                        | DF1700 | Ŷ |

|------------------------|--------|---|

| Basic Model Number     |        |   |

| Package Code           |        |   |

| P: 28-pin Plastic DIP  |        |   |

| U: 40-pin Plastic SOIC |        |   |

### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>pp</sub>                      | 0.3V to 7.0V                |

|---------------------------------------|-----------------------------|

| Input Voltage                         | 0.3 to Vpp +0.3V            |

| Soldering Temperature                 |                             |

| Soldering Time                        |                             |

| Storage Temperature                   | 40°C to +125°C              |

| Stresses above these ratings may perr | nanently damage the device. |

### ELECTROSTATIC DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

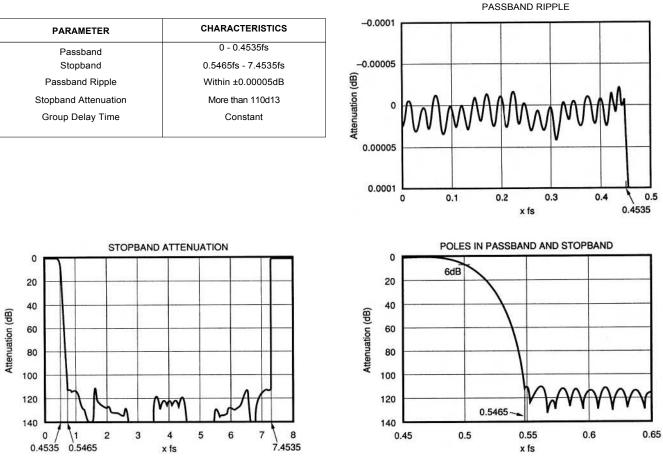

## THEORETICAL FILTER CHARACTERISTICS

### THEORY OF OPERATION

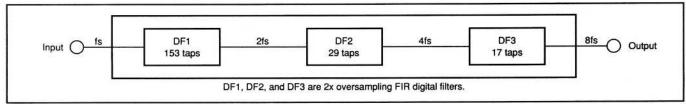

The DF1700 has dual filters. Each filter consists of three cascaded, 2x oversampling finite impulse response (FIR) filters as shown in Figure 1. The output of the first, 153-tap filter is again 2x oversampled by the second, 29-tap filter. This 4x oversampled data is again 2x oversampled by a third, 17-tap filter. This oversampling technique further separates the desired analog signal and the sampling frequency. This is

desirable because a low-pass filter is required at the output of a DAC to remove all unwanted frequency components caused by the sampling frequency. With the analog signal frequency further separated from the sampling frequency, a lower order analog filter with much better phase characteristics can be used at the output of the DAC without worrying about fold-over noise.

FIGURE 1. Block Diagram of Channel Filter.

### FUNCTIONAL DESCRIPTION

### SYSTEM CLOCK

The internal system clock of the DF1700 is generated by either a crystal oscillator connected across pins XTI and XTO driving the internal clock generator, or an external clock applied at pin XTI. Four different XTI clock frequencies can be obtained with the control of pins CKDV and CKSL. This will provide the correct clock period of the internal system clock as indicated in Table I. For XTI clock frequencies of 384fs and 512fs, the clock is divided by two for internal use. The system clock signal of the same frequency as pin XTI is available at pin CKO.

### DATA

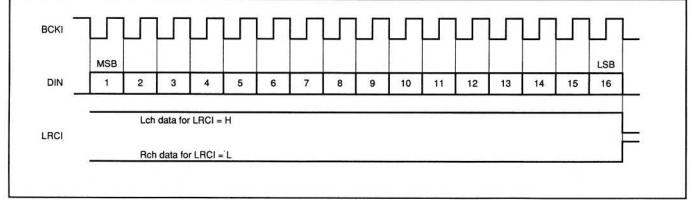

#### Serial Data Input

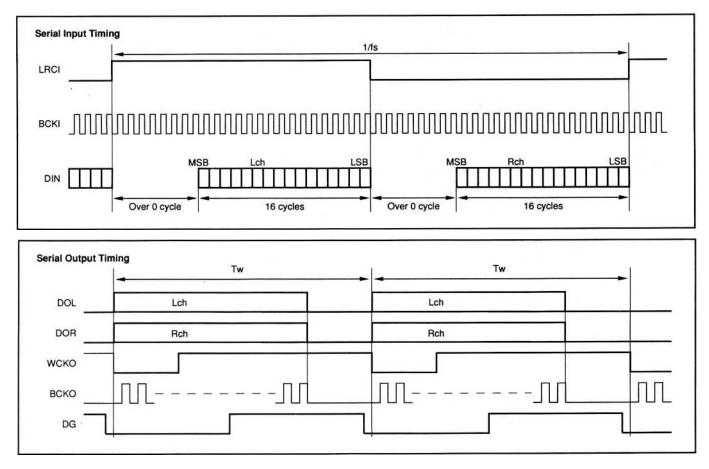

The 16-bit input data format is two's complement and MSB first. The serial data input timing is the rising edge of BCKI (Figure 2). Consequently the input serial data must be changed at the falling edge of BCKI. The input data is latched to the internal register at the edge of LRCI.

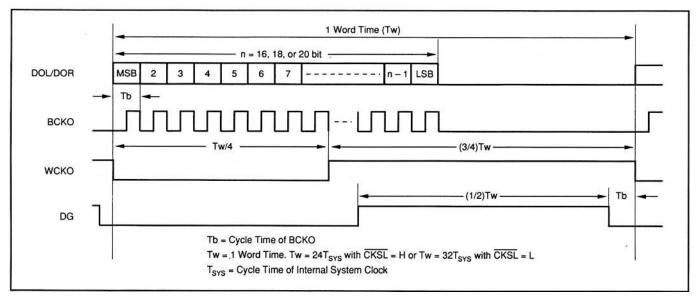

#### Serial Data Output

The serial data output mode is selected by pins  $\overline{OW18}$  and  $\overline{OW20}$  as shown in Table II.

The output data format is MSB first and either two's complement or complementary offset binary (COB). The format of output data is selected by the COB pin:

$\overline{\text{COB}} = \text{H}$  Two's complement

COB = L Complemented Offset Binary (COB)

The output data from the DF1700 can be fed directly to the data inputs of either the PCM1700 or PCM63 with the BCKO clock output serving as the input clock to these DACs. The data bits will be clocked into the DAC on the rising edges of BCKO (Figure 3).

| COND | ITION | XTI                      | CLOCK PERIOD OF       |  |  |

|------|-------|--------------------------|-----------------------|--|--|

| CKDV | CKSL  | CLOCK (F <sub>xi</sub> ) | INTERNAL SYSTEM CLOCK |  |  |

| н    | н     | 192fs                    | 1/F <sub>xi</sub>     |  |  |

| н    | L     | 256fs                    | 1/F <sub>xi</sub>     |  |  |

| L    | н     | 384fs                    | 2/F <sub>x1</sub>     |  |  |

| L    | L     | 512fs                    | 2/F <sub>x1</sub>     |  |  |

NOTE: fs = sampling frequency.

TABLE I. System Clock Frequency Selection.

| OW18 | OW20 | NO. OF OUTPUT DATA BITS |

|------|------|-------------------------|

| н    | н    | 16                      |

| L    | н    | 18                      |

| н    | L    | 20                      |

TABLE II. Programming the Number of Output Data Bits.

#### **CLOCK SYNCHRONIZATION**

The internal clock for the arithmetic circuitry and output interface is derived by the system clock from the XTI pin, and is independent of the input circuitry timing from the BCKI and LRCI input clocks. There are two synchronization modes: the Free-Running Mode and the Forced Synchronization Mode.

FIGURE 2. Input Timing Waveforms for Clocking Data into the DF1700.

FIGURE 3. Output Data Timing Waveforms.

#### Free-Running Mode (SYN = H)

No adjustment of the internal clock takes place for phase differences between the internal clock and the LRCI clock of up to  $\pm 3/8$  of the input data sample period (1/fs). Hence, internal timing is not affected even if jitter is present on the LRCI clock input, and no jitter or timing glitches appear on the data output. If the clock phase differences exceed the  $\pm 3/8$ fs limit, or if the RESET function is executed, the internal clock is synchronized to the rising edge of LRCI.

#### **Forced Synchronization Mode (SYN = L)**

In this mode the internal clock is resynchronized at each rising edge of LRCI. Note that device misoperation may occur if jitter in the LRCI input shortens the LRCI period below the required system clock period. Furthermore, if the LRCI period is too long, internal arithmetic operations will function correctly, but output timing is adversely affected.

The internal timing clock derived from the system clock is available at the FSCO pin.

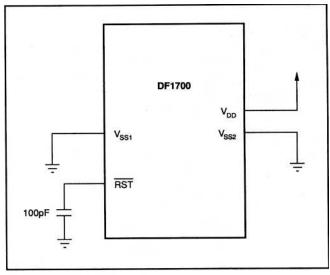

FIGURE 4. System Reset Circuit.

**SYSTEM RESET** (SYN = H). It is not necessary to reset in the forced synchroThe RESET function is useful for synchronizing the internal nization mode. Reset is also not required if the output timing arithmetic circuitry and output section clock with the LRCI needs not be synchronized with LRCI. Figure 4 shows the external input clock when operating in the free-running mode connection to reset the DF1700 on power-up.

# TIMING DIAGRAMS

### **APPLICATIONS**

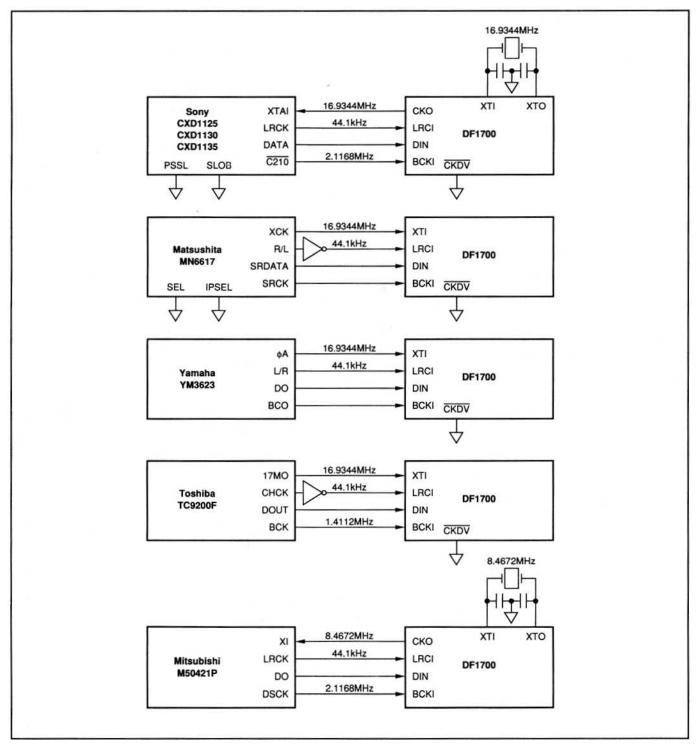

The most common application for the DF1700 is in high performance digital audio playback such as compact disc players. Digital information from a compact disc is often formatted using a digital interface format receiver chip ( DIFRC). The DF1700 can be interfaced directly to the output of many popular DIFRCs as shown in Figure 5.

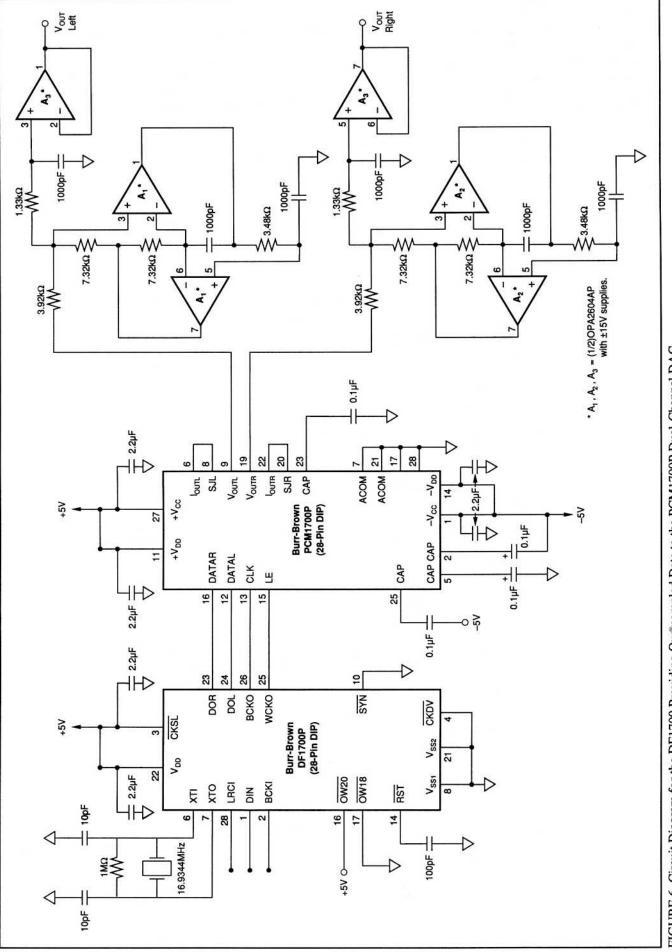

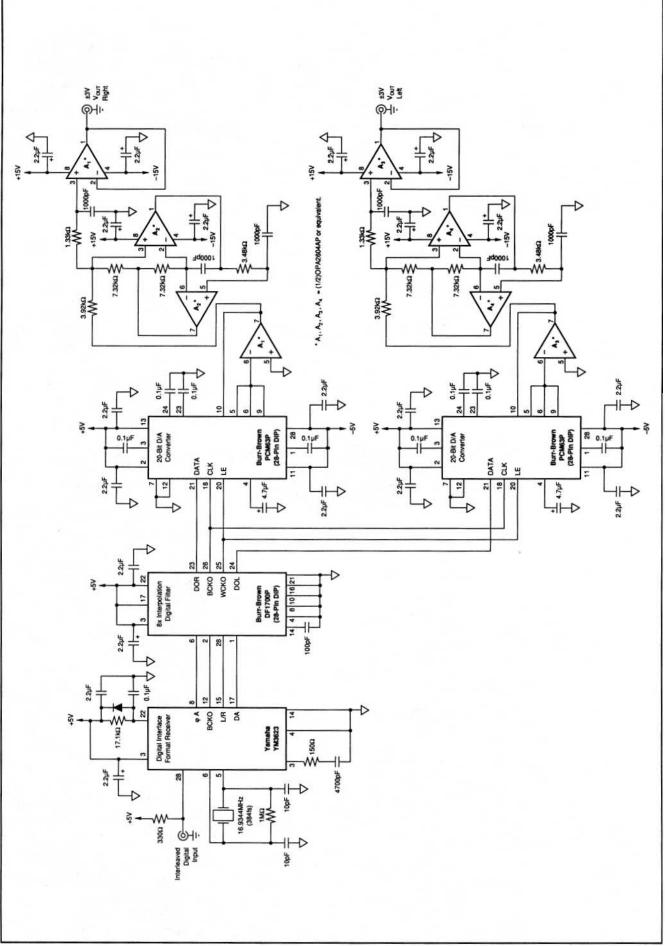

The fs data stream which has been formatted by the DIFRC is 8x oversampled by the DF1700 and separated into left and right channel data for input to the PCM1700 DAC (Figure 6). The analog stereo outputs from the PCM1700 each pass

through a three pole Generalized Immittance Converter (GIC) low-pass filter which has extremely low distortion and negligible phase shift. An evaluation board, the DEM 1143, is available from Burr-Brown for the PCM 1700/DF1700. This board has the features mentioned above as well as an AES/EBU interface and breadboard area for user experimentation. Figure 7 shows a similar circuit diagram with the DF1700 providing 8x oversampled data to a pair of PCM63 DACs.

FIGURE 5. Interfacing the DF1700 to Various Digital Interface Format Receiver Chips (DIFRCs).

FIGURE 6. Circuit Diagram for the DF1700 Providing Oversampled Data to the PCM1700P Dual-Channel DAC.

FIGURE 7. Circuit Diagram for the DF1700 Providing Oversampled Data to a Pair of PCM63P DACs.